If you use VHDL RTL code for your clock divider you can easily port your VHDL code on different FPGA or ASIC technology. At the end of data transmission the parallelized input is available on.

A Low Pass Fir Filter For Ecg Denoising In Vhdl Fpga4student Com

Design development and implementation of code integration processes release pipelines and deployment strategies.

. Grtgrsteruegwertfwt rgrdsydrgd ryey ryhgey. VHDL code for 8-bit Comparator 9. The input parallel data will be send using tx_start input signal.

Clash is a functional hardware description language that borrows both its syntax and semantics from the functional programming language HaskellIt provides a familiar structural design approach to both combinational and synchronous sequential circuits. PWM Generator in VHDL with. The Vitis Model Composer AI Engine HLS and HDL libraries within the Simulink environment enable the rapid design exploration of an algorithm and accelerate the path to.

The FSM goes to ST_TX_RX state for a programmed number of clock cycles. Vitis Model Composer is a Model-Based Design tool that enables rapid design exploration within the MathWorks MATLAB and Simulink environment and accelerates the path to production on Xilinx devices through automatic code generation. VHDL code for Matrix Multiplication 6.

How to load a text file into FPGA using VHDL 10. VHDL code for digital alarm clock on FPGA 8. Design and analyze digital filters from basic single-rate lowpass or highpass to more advanced FIR and IIR designs including multirate multistage and adaptive filters.

GCD Calculator ESD Chapter2. VHDL code for 8-bit Microcontroller 5. VHDL code for 8-bit Comparator 9.

This modulation technique is modeled using VHDL code. You can visualize magnitude phase group delay and impulse response as well as evaluate filter performance including stability and phase linearity. VHDL code for Matrix Multiplication 6.

VHDL code for 8-bit Microcontroller 5. VHDL code for digital alarm clock on FPGA 8. This project improves the performance of FIR filter by designing it with distributed arithmetic of three dimensional lookup table instead of multiplier.

Design of Multi Value Logic Using Quantum Dot Gate FET. Vitis Model Composer provides a library of performance-optimized blocks for design and implementation of DSP algorithms on Xilinx devices. Enter the email address you signed up with and well email you a reset link.

During the data transmission MISO input is sampled on the internal shift register. How to load a text file into FPGA using VHDL 10. VHDL code for Switch Tail Ring Counter 7.

Version 07 Bug fixes. VHDL code for FIR Filter 4. Filter designs can be analyzed and simulated to evaluate.

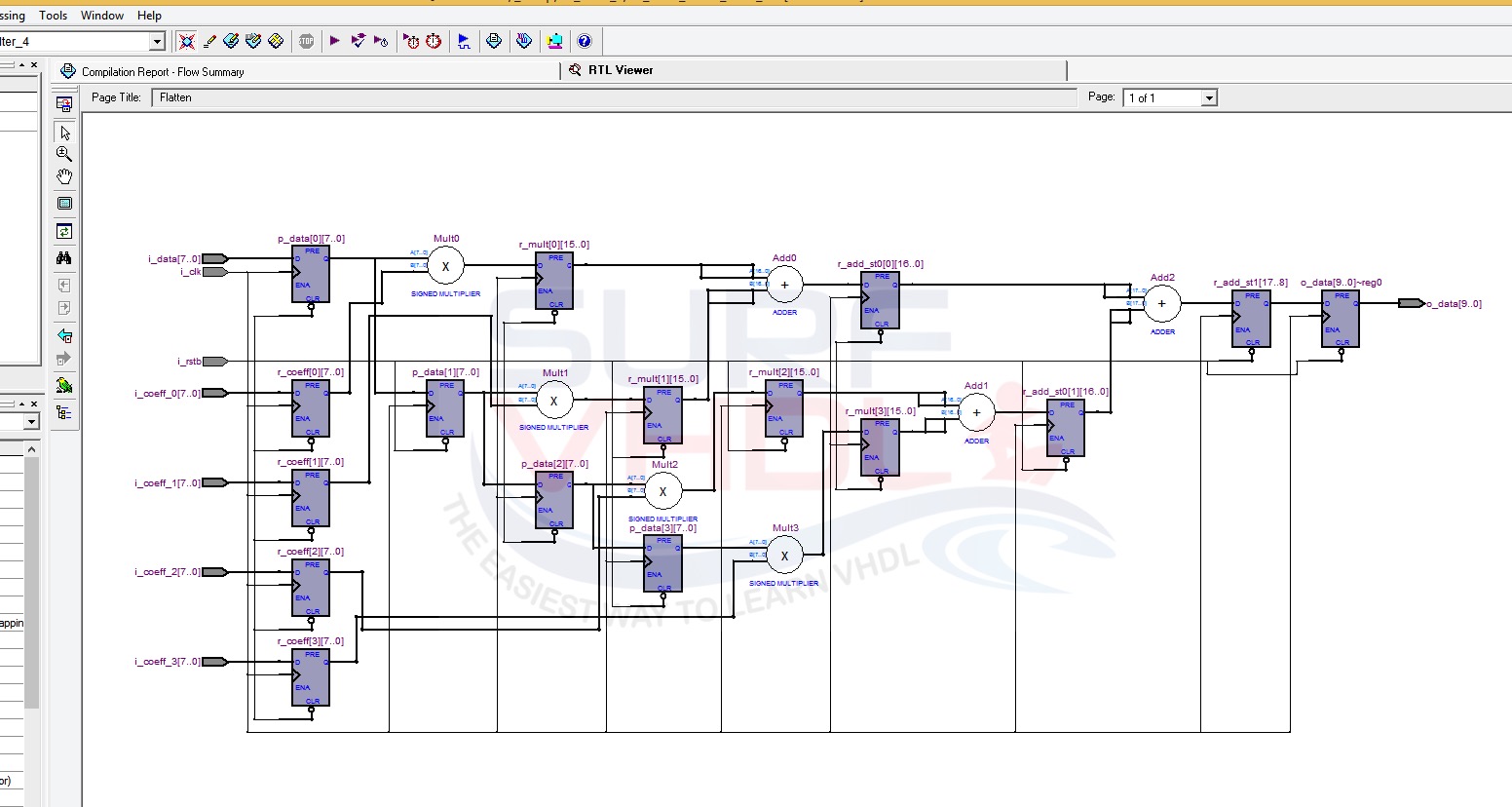

In this case the FPGA entity fir_filter_pad is a simple wrapper for the component. The SPI controller VHDL code will implement the FSM described in Figure 6. Architecture behav of DeBounce is--the below constants decide the working parameters--the higher this is the more longer time.

Windows95 98 Me NT 2K and XP 206 KB 07 July 26th 2004. VHDL code for FIR Filter 4. The filter coefficients are now quantizied in float 16-bit or 8-bit.

Learn rapid design exploration using Vitis Model Composer. VHDL code for FIFO memory 3. A comparison of the coding styles between the RTL modeling and Algorithm level modeling highlights the different techniques.

There are no professors associated with this course for the 2021-2022 academic year. Every VHDL design description consists of at least one entity. VHDL code for IIR filter.

VHDL code for Full Adder 12. 08 December 6th 2004. The Clash compiler transforms these high-level descriptions to low-level synthesizable VHDL Verilog or.

You can design your DSP algorithms and iterate through them using high-level performance-optimized blocks and. The FIR digital filter algorithm is simulated and synthesized using VHDL. Entity DeBounce is port Clock.

Synthezis in VHDL speed or size optimization with a Resources Usage. AddRemove PoleZero possibilities Filter conversion from S domain to Z domain. VHDL code for D Flip Flop 11.

Figure 29-211 FSMD Modeling. This course is not scheduled for the 2021-2022 academic year. You can use the code above for your VHDL clock design if you need a clock divider by an integer in your design without using the FPGA PLLDCM.

VHDL code for D Flip Flop 11. VHDL code for DeBouncer circuit. VHDL code for Switch Tail Ring Counter 7.

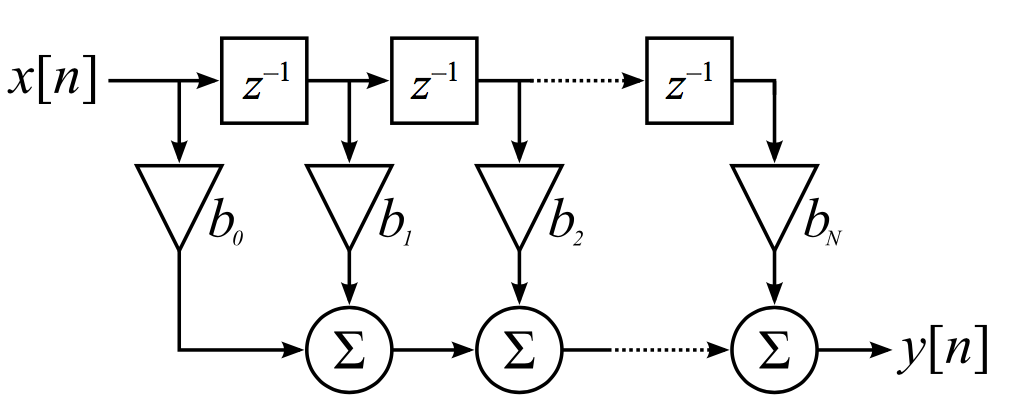

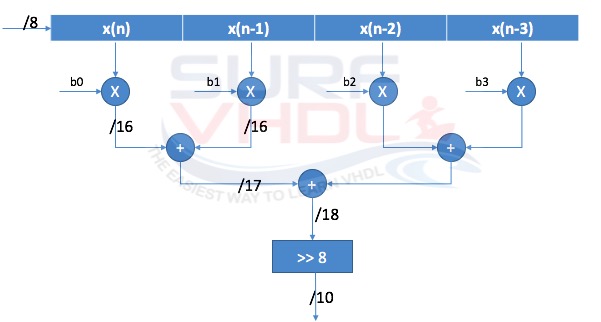

Design of Finite Impulse Response Filter Using Distributed Arithmetic of Lookup Table. Finite impulse response FIR filters Thursday Feb 10th 2022 As an FPGA designer you have the freedom to implement the finite impulse response FIR filter either parallel or in series.

Fir Filter Vhdl Logic Engineering And Component Solution Forum Techforum Digi Key

How To Implement Fir Filter In Vhdl Surf Vhdl

Digital Filter Fir Using Vhdl Forum For Electronics

How To Implement Fir Filter In Vhdl Surf Vhdl

Pdf Vhdl Generation Of Optimized Fir Filters Semantic Scholar

Fpga Fir Filter Circuit Architecture And Vhdl Design Youtube

A Low Pass Fir Filter For Ecg Denoising In Vhdl Fpga4student Com

0 comments

Post a Comment